Naha anjeun terang kumaha ngabéréskeun masalah EMI nalika desain PCB multi-lapisan?

Hayu atuh ngabejaan Anjeun!

Aya loba cara pikeun ngajawab masalah EMI.métode suprési EMI modern ngawengku: ngagunakeun palapis suprési EMI, milih bagian suprési EMI luyu jeung desain simulasi EMI.Dumasar kana perenah PCB paling dasar, makalah ieu ngabahas fungsi tumpukan PCB dina ngadalikeun radiasi EMI jeung kaahlian desain PCB.

beus kakuatan

Luncat tegangan kaluaran IC tiasa digancangan ku nempatkeun kapasitansi anu pas caket pin kakuatan IC.Sanajan kitu, ieu teu tungtung masalah.Kusabab réspon frékuénsi kawates tina kapasitor, mustahil pikeun kapasitor ngahasilkeun kakuatan harmonik anu dipikabutuh pikeun ngajalankeun kaluaran IC sacara bersih dina pita frékuénsi pinuh.Sajaba ti éta, tegangan fana kabentuk dina beus kakuatan bakal ngabalukarkeun turunna tegangan dina duanana tungtung induktansi jalur decoupling.Tegangan transien ieu mangrupikeun sumber gangguan EMI modeu umum utama.Kumaha urang bisa ngajawab masalah ieu?

Dina kasus IC on circuit board urang, lapisan kakuatan sabudeureun IC bisa dianggap salaku kapasitor frékuénsi luhur alus, nu bisa ngumpulkeun énergi bocor ku kapasitor diskrit nu nyadiakeun énergi frékuénsi luhur pikeun kaluaran bersih.Sajaba ti éta, induktansi tina lapisan kakuatan alus leutik, jadi sinyal fana disintésis ku induktor oge leutik, sahingga ngurangan EMI mode umum.

Tangtosna, sambungan antara lapisan catu daya sareng pin catu daya IC kedah pondok-gancang, sabab ujung rising sinyal digital langkung gancang sareng langkung gancang.Éta leuwih alus pikeun nyambungkeun eta langsung ka Pad mana IC kakuatan pin lokasina, nu kudu dibahas misah.

Pikeun ngadalikeun modeu umum EMI, lapisan kakuatan kedah janten pasangan lapisan kakuatan anu dirancang kalayan saé pikeun ngabantosan decouple sareng gaduh induktansi anu cukup handap.Sababaraha urang bisa nanya, kumaha alus éta?Jawabanna gumantung kana lapisan kakuatan, bahan antara lapisan, sareng frékuénsi operasi (nyaéta, fungsi waktos naékna IC).Sacara umum, jarak lapisan kakuatan nyaéta 6mil, sareng interlayer mangrupikeun bahan FR4, janten kapasitansi sarimbag per inci pasagi lapisan kakuatan sakitar 75pF.Jelas, nu leutik jarak lapisan, nu leuwih gede capacitance nu.

Henteu seueur alat anu gaduh waktos naékna 100-300ps, tapi dumasar kana tingkat pangembangan IC ayeuna, alat-alat anu waktos naékna dina kisaran 100-300ps bakal ngeusian saimbang anu luhur.Pikeun sirkuit kalawan 100 ka 300 PS kali naékna, 3 mil lapisan spasi euweuh lumaku pikeun kalolobaan aplikasi.Dina waktos éta, perlu pikeun ngadopsi téknologi delamination kalayan jarak interlayer kirang ti 1mil, sareng ngagentos bahan diéléktrik FR4 sareng bahan kalayan konstanta diéléktrik anu luhur.Ayeuna, keramik jeung plastik potted bisa minuhan sarat desain 100 mun 300ps naékna sirkuit waktu.

Sanajan bahan jeung métode anyar bisa dipaké dina mangsa nu bakal datang, umum 1 nepi ka 3 ns naékna sirkuit waktu, 3 nepi ka 6 mil lapisan spasi, jeung bahan diéléktrik FR4 biasana cukup pikeun nanganan harmonik luhur-tungtung jeung nyieun sinyal fana cukup low, nyaeta. , modeu umum EMI bisa ngurangan pisan low.Dina makalah ieu, conto desain PCB layered stacking dibikeun, sarta jarak lapisan dianggap 3 ka 6 mil.

shielding éléktromagnétik

Ti sudut pandang routing sinyal, strategi layering alus kudu nempatkeun sagala ngambah sinyal dina hiji atawa leuwih lapisan, nu gigireun lapisan kakuatan atawa pesawat taneuh.Pikeun catu daya, strategi layering anu saé nyaéta yén lapisan kakuatan padeukeut sareng pesawat taneuh, sareng jarak antara lapisan kakuatan sareng pesawat taneuh kedah sakedik-gancang, anu kami sebut strategi "layering".

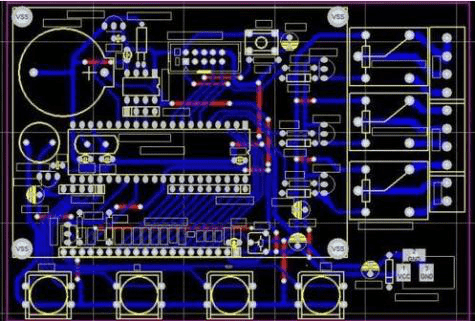

tumpukan PCB

Jenis strategi tumpukan anu tiasa ngabantosan tameng sareng ngirangan EMI?Skéma susun lapis di handap ieu nganggap yén arus catu daya ngalir dina lapisan tunggal sareng tegangan tunggal atanapi sababaraha voltase disebarkeun dina bagian anu béda dina lapisan anu sami.Kasus sababaraha lapisan kakuatan bakal dibahas engké.

piring 4-ply

Aya sababaraha masalah poténsial dina desain laminates 4-ply.Anu mimiti, sanajan lapisan sinyal aya dina lapisan luar jeung kakuatan sarta pesawat taneuh aya dina lapisan jero, jarak antara lapisan kakuatan jeung pesawat taneuh masih badag teuing.

Upami sarat biaya mangrupikeun anu munggaran, dua alternatif di handap ieu pikeun papan 4-ply tradisional tiasa dipertimbangkeun.Duanana tiasa ningkatkeun kinerja suprési EMI, tapi aranjeunna ngan cocog pikeun kasus dimana dénsitas komponén dina dewan cukup lemah sareng aya cukup wewengkon sabudeureun komponén (pikeun nempatkeun palapis tambaga diperlukeun pikeun catu daya).

Anu kahiji nyaéta skéma anu dipikaresep.Lapisan luar PCB sadayana lapisan, sareng dua lapisan tengah mangrupikeun lapisan sinyal / kakuatan.Catu daya dina lapisan sinyal dialihkeun ku garis anu lega, anu ngajantenkeun impedansi jalur catu daya ayeuna rendah sareng impedansi jalur mikrostrip sinyal rendah.Tina sudut pandang kontrol EMI, ieu mangrupikeun struktur PCB 4-lapisan anu pangsaéna.Dina skéma kadua, lapisan luar mawa kakuatan jeung taneuh, sarta dua lapisan tengah mawa sinyal.Dibandingkeun sareng papan 4-lapisan tradisional, perbaikan skéma ieu langkung alit, sareng impedansi interlayer henteu saé sapertos papan 4-lapisan tradisional.

Lamun impedansi wiring kudu dikawasa, skéma stacking luhur kudu ati pisan iklas wiring handapeun pulo tambaga catu daya jeung grounding.Sajaba ti éta, pulo tambaga dina catu daya atawa stratum kudu interconnected saloba mungkin pikeun mastikeun konektipitas antara DC jeung frékuénsi low.

piring 6-ply

Lamun dénsitas komponén dina dewan 4-lapisan badag, piring 6-lapisan hadé.Sanajan kitu, pangaruh shielding sababaraha skéma stacking dina desain dewan 6-lapisan teu cukup alus, sarta sinyal transien tina beus kakuatan teu ngurangan.Dua conto dibahas di handap.

Dina kasus nu pertama, catu daya sareng taneuh disimpen dina lapisan kadua sareng kalima masing-masing.Alatan impedansi tinggi tina catu daya clad tambaga, éta pisan nguntungkeun pikeun ngadalikeun radiasi EMI mode umum.Nanging, tina sudut pandang kontrol impedansi sinyal, metode ieu leres pisan.

Dina conto kadua, catu daya sareng taneuh disimpen dina lapisan katilu sareng kaopat masing-masing.Desain ieu solves masalah impedansi clad tambaga tina catu daya.Kusabab kinerja shielding éléktromagnétik goréng tina lapisan 1 jeung lapisan 6, mode diferensial EMI naek.Lamun jumlah garis sinyal dina dua lapisan luar téh pangsaeutikna jeung panjang garis pisan pondok (kirang ti 1/20 tina panjang gelombang harmonik pangluhurna sinyal), desain bisa ngajawab masalah mode diferensial EMI.Hasilna nunjukkeun yén suprési mode diferensial EMI hususna saé nalika lapisan luar dieusian ku tambaga sareng daérah clad tambaga dibumikeun (unggal 1/20 interval panjang gelombang).Sakumaha didadarkeun di luhur, tambaga kudu diteundeun

waktos pos: Jul-29-2020